# Model 560-5907-U PCI-SG-2U Model 560-5908-U GPS-PCI-2U

PCI Plug-In Card

Generator Synchronized Generator GPS Synchronized Generator

Serial Number\_

Part #: 097-00560-01, Rev. A November, 2004

Model 560-5907-U PCI-SG-2U

Model 560-5908-U GPS-PCI-2U

## Table of Contents

| Preface                                                    |

|------------------------------------------------------------|

| Conventions1                                               |

| Errata1                                                    |

| Limited Warranty                                           |

| Limitation of Liability2                                   |

| Proprietary Notice                                         |

| Introduction                                               |

| General Information                                        |

| Mode Select                                                |

| Generator Mode                                             |

| Synchronized Generator Mode                                |

| GPS Mode (Model 560-5908-U only)                           |

| Software Time Capture                                      |

| Event Time Capture                                         |

| Time Zone Adjustment                                       |

| Daylight Saving Time Adjustment                            |

| Leap Second                                                |

| Phase Compensation (Cable Length Adjustment)               |

| AM Timecode Output                                         |

| DC Timecode Output                                         |

| Rate Generator Output   5                                  |

| Rate Synthesizer Output                                    |

| 1 PPS Output                                               |

| Time Compare Pulse Output                                  |

| BNC Output Source Select                                   |

| Antenna Position Setup (560-5908-U only)                   |

| Stored Configuration                                       |

| Time Quality Flags                                         |

| On Card Status LEDs                                        |

| DS1 (top):                                                 |

| DS2 (middle):                                              |

| DS3 (bottom):                                              |

| 12 Volt Antenna Feed (560-5908-U only)                     |

| Physical Specifications                                    |

| Environmental Specifications                               |

| Power Specifications                                       |

| Antenna Specifications (560-5908-U)                        |

| Signal / Timing Specifications (560-5907-U and 560-5908-U) |

| External Event / 1 PPS Reference Input                     |

| GPS Timing Specifications (560-5908-U) 10                  |

| Output Signal Specifications                               |

| Amplitude-modulated Generator Code Output    11            |

| IRIG-B DC Generator Code Output                                         | 11 |

|-------------------------------------------------------------------------|----|

| Time Compare Output                                                     | 11 |

| 1 PPS Output                                                            |    |

| Rate Generator Output                                                   | 11 |

| Rate Synthesizer Output                                                 |    |

| General Specifications                                                  |    |

| Factory Defaults                                                        |    |

| 560-5907-U/560-5908-U Configuration                                     |    |

| 560-5907-U/560-5908-U Factory Installed Hardware Jumper Configuration . | 14 |

| Installation                                                            |    |

| Installing the Card                                                     |    |

| Installation                                                            |    |

| Antenna Location and Installation (GPS only)                            |    |

| Use of a Splitter                                                       |    |

| Lead-In Cable                                                           |    |

| TTPciPanel Software Requirements and Installation                       | 16 |

| Minimum System Requirements                                             | 16 |

| User Notes                                                              | 16 |

| Optional Software Development Kit                                       |    |

| Installing TTPciPanel                                                   |    |

| Upgrading from TTPciPanel                                               |    |

| Starting TTPciPanel                                                     |    |

| Quickstart Guide to Operating TTPciPanel                                |    |

| TTPciPanel Screen Descriptions                                          |    |

| Main Panel                                                              |    |

| Device Tab                                                              |    |

| General Tab                                                             |    |

| Time Tab                                                                |    |

| GPS Tab                                                                 |    |

|                                                                         |    |

| Operation                                                               | 23 |

| General Operation                                                       | 23 |

| Time Preset                                                             |    |

| Generator Mode                                                          |    |

| Synchronized Generator Mode                                             |    |

| PCI Card Control/Status Registers (Overview)                            |    |

| PCI Card Registers                                                      |    |

| PCI Configuration Header Region                                         |    |

| PLX 9050 Local Configuration Registers                                  |    |

| Hardware Control Register                                               |    |

| Software Time Capture Register                                          |    |

| Hardware Status Register                                                |    |

| Antenna Position Register (560-5908-U only)                             |    |

| Configuration #1 Register                                               |    |

| Diagnostic Register                                                     | 32 |

| Time Zone Offset Register                                  | 33 |

|------------------------------------------------------------|----|

| Phase Compensation / Factory Calibration Registers         | 34 |

| Rate Synthesizer Register                                  | 35 |

| Configuration #2 Register                                  | 36 |

| Time Compare Register                                      | 37 |

| Preset Time Register                                       | 38 |

| Preset Position Register (560-5908-U only)                 | 39 |

| Event Time Capture Register                                |    |

| Satellite Signal Strength Register (560-5908-U only)       |    |

| Satellite Signal Strength Update Status                    |    |

| IRIG AM AGC Delays                                         |    |

| Software Version Register                                  |    |

| Examples                                                   |    |

| Generator Mode                                             |    |

| Selecting the Mode                                         |    |

| Setting Time                                               |    |

| Status                                                     |    |

| Start/Stop                                                 |    |

| Registers Used in Generator Mode                           |    |

| Synchronized Generator - IRIG AM                           |    |

| Procedure                                                  |    |

| Status                                                     |    |

| Registers Used in Synchronized Generator mode (IRIG-AM)    |    |

| Synchronized Generator - IRIG DC                           |    |

| Procedure                                                  |    |

| Status                                                     |    |

| Registers Used in Synchronized Generator mode (IRIG DC)    |    |

| Synchronized Generator – 1 PPS                             |    |

| Procedure                                                  |    |

| Status                                                     |    |

| Registers Used in Synchronized Generator mode (1 PPS)      |    |

| Synchronized Generator – GPS (560-5908-U only)             |    |

| Procedure                                                  |    |

| Status                                                     |    |

| Registers Used in Synchronized Generator mode (GPS-PCI-2U) |    |

| Time Capture                                               |    |

| Software Time Capture                                      |    |

| Application                                                |    |

| Procedure                                                  |    |

| Event Time Capture                                         |    |

| Application                                                |    |

| Procedure                                                  |    |

|                                                            |    |

| Customer Support                                           |    |

|                                                            |    |

| Index                                                      | 53 |

| · · · · · · · · · · · · · · · · · · ·                      |    |

Table of Contents

iv

## Preface

## Conventions

The conventions used in this manual are:

| $\bigcirc$ | = | Tips and clarifications.                                                                                                 |

|------------|---|--------------------------------------------------------------------------------------------------------------------------|

| WARNING    | = | Actions to prevent equipment damage.                                                                                     |

| Bold       | = | Used to show messages, menu items, etc., that appear on a computer screen. For example, click on <b>Submit Changes</b> . |

| text       | = | Used to indicate text you should enter with your keyboard, <i>exactly</i> as printed.                                    |

| text       | = | Used to display output character strings.                                                                                |

## Errata

Errata are available on the CD ROM supplied with the equipment. The errata file name is "Errata.pdf".

## **Limited Warranty**

Each new product manufactured by Symmetricom is warranted for defects in material or workmanship for a period of one year from date of shipment ("Limited Warranty"). Defects in material or workmanship found within that period will be replaced or repaired, at Symmetricom's option, without charge for material or labor, provided the customer returns the equipment, freight prepaid, to the Symmetricom factory under this limited warranty. Symmetricom will return the repaired equipment, freight prepaid, to the customer's facility. This one year Limited Warranty does not apply to any software or to any product not manufactured by Symmetricom.

If on-site warranty repair or replacement is required, the customer will be charged the then current field service rate for portal-to-portal travel time plus actual portal-to-portal travel charges. There is no charge for on-site warranty repair labor.

Preface

Products not manufactured by Symmetricom but included as integral part of a system (e.g. peripherals, options) are warranted for 90 days, or longer as provided by the original equipment manufacturer, from date of shipment.

Aside from the Limited Warranty set forth above, Symmetricom makes no other warranties, express or implied, of merchantability, fitness for purpose or of any other kind or description whatsoever.

By purchasing any product manufactured by Symmetricom, the buyer consents to and agrees with Symmetricom that as a result of the exclusion of all warranties, expressed or implied, of merchantability, fitness for purpose, or otherwise, except for the limited one-year warranty for defects in material and workmanship for products manufactured by Symmetricom, that the Buyer has the sole responsibility to assess and bear all losses relating to (1) the ability of the product or products purchased to pass without objection under the contract description among merchants and buyers in the trade; (2) the conformity of the product or products to fair average quality within its contract description; (3) the fitness of the product for the ordinary purposes for which such product is used; (4) the consistency of quality and quantity within each unit of product or products and among all units involved; (5) the adequacy of containers, packaging and labeling of the product or products; (6) the conformity of the product, promises or affirmations of fact (if any) made on its label or container; and (7) the conformity of the product to standards of quality observed by other merchants in the trade with respect to products of similar description.

## Limitation of Liability

By purchasing any product from Symmetricom, the Buyer consents to and agrees that the Buyer's sole and exclusive remedy for any damages or losses incurred by the Buyer as a result of Symmetricom's breach of its one-year Limited Warranty for defects in materials and workmanship or otherwise in connection with any claim respecting the product shall be limited to the repair or replacement of the product or a refund of the sales price of the product.

In no event shall the Buyer be entitled to recover consequential damages or any other damages of any kind or description whatsoever.

## **Proprietary Notice**

This document, whether patentable or non-patentable subject matter, embodies proprietary and confidential information and is the exclusive property of Symmetricom, Inc. It may not be reproduced, used or disclosed to others for any purpose except that for which it is purchased or loaned.

## Introduction

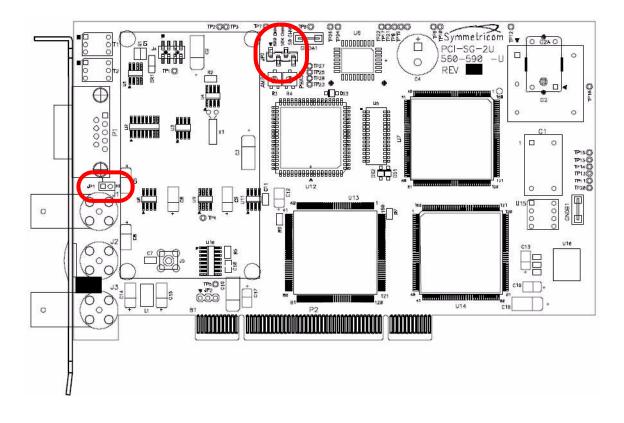

## 1.1 General Information

The Symmetricom model 560-5907-U (PCI-SG-2U) and 560-5908-U (GPS-PCI-2U) generator cards are high-performance, 32-bit, PCI plug-in cards. They provide precise time synchronization to the host computer over the PCI bus. They operate at 33 MHz, and are fully compliant with the PCI Local Bus Specification, Revision 2.2, and are compatible with Revision 2.3. The cards support both the 3.3 V and 5 V signaling environments, defined by the PCI Local Bus Specification. The cards are considered universal add-in cards that are capable of detecting the signaling environment and adapting themselves to that environment.

These products may be used in either Generator or Synchronized Generator mode, supplying precise time (100's nanoseconds through thousands of years) to the host computer. When the card is operating as a Synchronized Generator the output signals are synchronized to the timing reference. The PCI card phase locks to the timing reference and controls the on-board oscillator to remove frequency errors. If the timing reference is lost, the PCI card continues to increment time and output timing signals based upon the on-board oscillator's frequency (flywheeling).

The PCI card includes a real-time clock. This feature has an automatic, maintenance-free, capacitor backup that enables the PCI card to continue incrementing time in the event of a power failure. The capacitor powers the real-time clock for a minimum of 48 hours.

All sections of this manual are applicable to all models except where noted.

## 1.1.1 Mode Select

The PCI card operating modes that may be selected are as follows:

## Generator Mode

Use this mode when an external reference is not used. In the Generator mode, the time may be started, stopped and preset via the PCI bus. In this mode, the Generator time accuracy is a function of the drift rate of the on-board oscillator.

## Synchronized Generator Mode

The Model 560-5907-U and 560-5908-U cards may be synchronized by one of the following input references:

| IRIG-B (AM) | Year entry required          |

|-------------|------------------------------|

| IRIG-A (AM) | Year entry required          |

| IRIG-B (DC) | Year entry required          |

| IRIG-A (DC) | Year entry required          |

| 1 PPS       | Complete time entry required |

In the Synchronized Generator mode, the card is synchronized by an external reference. The on-board oscillator is disciplined to this input reference so that the card's drift rate is a function of the external reference.

## GPS Mode (Model 560-5908-U only)

The Model 560-5908-U card may be synchronized by any of previously listed references or by GPS. This mode allows the Global Positioning System to automatically synchronize the PCI card to UTC time. The GPS Module assumes a moderate dynamic environment (LAND mode, velocity < 120 knots). The fix mode is AUTO 2-D/3-D and is preferable for most LAND applications.

## 1.1.2 Software Time Capture

When time is requested by software, the time from 100's of nanoseconds through thousands of years is captured when the request is received. The captured time is available to the host in packed BCD format and is independent of the Event Capture registers. The captured time will be compensated for local offset and daylight saving time if those settings have been made. The Software Time Capture Logic processes requests as fast as every 200 ns.

There is a maximum 150 ns delay from the time that a request is received until the time is ready.

## 1.1.3 Event Time Capture

The time from 100's of nanoseconds through thousands of years is captured when the specified edge (rising or falling) of the event signal occurs. The captured time is available to the host in packed BCD format. The Event Time Capture may be selected to trigger by one of the following signals:

- External Event

- PCI card Rate Generator

- PCI card Rate Synthesizer

- PCI card Time Compare

When an event occurs, the time is latched into the Event Time Registers and the Event Status Bit is set at location 0F8. If interrupts are enabled, a interrupt occurs concurrently with the status bit being set. Although the event capture can handle rates faster than most PC's can handle, the event hardware keeps only one time until the Event Status Clear Bit is set at 0F8.

## 1.1.4 Time Zone Adjustment

The Time Zone Offset Register is used to convert UTC time (either the time from the input reference or the generator) to Standard Time. The range of the time zone adjustment is from -12:59 to +12:59 hours.

## 1.1.5 Daylight Saving Time Adjustment

The card provides the ability to automatically handle DST transitions in any mode if DST is enabled. The transition takes place at 2:00 a.m. local time on the first Sunday in April and the last Sunday in October.

## 1.1.6 Leap Second

The PCI card will add an extra second at the end of the current UTC day if the Leap Second setting is made.

## 1.1.7 Phase Compensation (Cable Length Adjustment)

The PCI card has the ability to correct its timing outputs for phase delay caused by cabling. The range of compensation is from -800 to +800  $\mu$ s with 100's of nanoseconds resolution. Positive adjustments moves the PCI Card outputs earlier in time. Negative adjustments move the PCI Card outputs later in time.

## 1.1.8 AM Timecode Output

The PCI card provides IRIG-B122 code as an output. The output may be selected to be on J1 "CODE OUT" BNC. The output voltage is factory set to 3 Vp-p into 600 ohms with a ratio of 3:1.

## 1.1.9 DC Timecode Output

The PCI card provides IRIG-B002 code as an RS-422 level output on the D9, pin 8 (+), pin 9 (–). The DC Timecode output may also be selected to be on J1 "CODE OUT" BNC.

## 1.1.10 Rate Generator Output

The Rate Generator outputs a signal at pin 7 of the D9 connector, output may also be selected on J1 "CODE OUT" BNC, with one of the following rates:

Disabled, 1 PPS, 10 PPS, 100 PPS, 1k PPS, 10k PPS, 100k PPS, 1 MPPS, 5 MPPS or 10 MPPS.

The Rate Generator signal is synchronous with the board timing and the rising edge is on time. With the exception of the 10 MPPS rate, the rate generator outputs have a 50% duty cycle. The 10 MPPS output is a function of the on-board oscillator's duty cycle (typically, 40-60%). The Rate Generator bit of the Hardware Status Register (location 0xFE) indicates when a Rate Generator rising edge has occurred

## 1.1.11 Rate Synthesizer Output

The Rate Synthesizer may be output on pin 6 of the D9 connector, which is selectable for either Time Compare or Rate Synthesizer output. The Time Compare may also be selected to be output on J1 "CODE OUT" BNC.

The Rate Synthesizer may be selected to output rates from 1 PPS to 1 MPPS in 1 PPS increments. The Output is a squarewave (50% duty cycle) and the edge may be selected to be either rising or falling on time. The Rate Synthesizer bit of the Hardware Status Register (location 0xFE) indicates when the rising edge (not on-time edge) of the Rate Synthesizer has occurred. A PCI interrupt is generated on occurrence of the rising edge, if enabled.

## 1.1.12 1 PPS Output

This PCI card output is on pin 5 of the D9 connector. The 1 PPS may also be selected to be on J1 "CODE OUT" BNC. This signal is rising edge on time and has a 50% duty cycle. A PCI interrupt is generated on occurrence of the rising edge, if enabled.

## 1.1.13 Time Compare Pulse Output

The Time Compare may be output on pin 6 of the D9 connector, which is selectable for either Time Compare or Rate Synthesizer output. The Time Compare may also be selected to be output on J1 "CODE OUT" BNC.

The Time Compare Output generates a 1 ms pulse that occurs when the Time Compare setting matches the PCI card's time. Time Compare can be used to output pulses at regular time intervals. The Time Compare bit of the Hardware Status Register (location 0xFE) indicates when a Time Compare has occurred. A PCI interrupt is generated on occurrence of the rising edge, if enabled.

## 1.1.14 BNC Output Source Select

J1 "CODE OUT" BNC may be selected to output any of the following signals:

- IRIG-B AM (IRIG-B122)

- IRIG-B DC (IRIG-B002)

- Rate Generator

- Rate Synthesizer

- Time Compare

- 1 PPS

## 1.1.15 Antenna Position Setup (560-5908-U only)

In GPS mode, the user's position (longitude, latitude, and altitude) may be preset to speed satellite acquisition at turn on (refer to register, location 0x164 through 0x173).

## 1.1.16 Stored Configuration

Several parameters are retained in Electrically Erasable Programmable Read Only Memory (EEPROM) while the PCI card power is off. The following parameters define the configuration of the PCI card:

- Rate Generator Output

- Rate Synthesizer Output

- Phase Compensation

- Current Year

- Operating Mode

- Synchronized Generator Reference

- Daylight Savings Time Flag\Time Zone

- Time Compare Settings

- External Event Setup

- Time Quality Flag Usage

Both the Daylight Savings Time (DST) flag and Time Zone are saved, however, the Symmetricom driver resets both to 0 at start-up.

Note that the EEPROM has a finite number of write cycles (100,000).

## 1.1.17 Time Quality Flags

When operating in IRIG Synchronized Generator mode, the PCI card may be set to read the lock and four time quality status bits from a Symmetricom IRIG source. These five bits are encoded in the Control Field (P5) on various models of Symmetricom clocks. The status bits will allow the user of the PCI card to decide whether the IRIG source should be used for synchronization (see Section 3.3.8)

## 1.1.18 On Card Status LEDs

## DS1 (top):

This LED blinks at a 1 PPS rate when the PCI-SG-2U is in Synchronized Generator mode and has locked to the input reference. This LED is OFF when in Generator mode or when unlocked to the input reference in Synchronized Generator mode.

## DS2 (middle):

This LED is ON when the Rate Synthesizer PLL is locked to the master 10 MHz on-board oscillator. This LED blinks at a 1 PPS rate when the PLL is unlocked. If the Rate Synthesizer is being used, contact service for assistance (if not used, ignore the LED).

## DS3 (bottom):

This LED is ON at turn on and OFF when the FGPA has been successfully programmed.

#### 1.1.19 12 Volt Antenna Feed (560-5908-U only)

The Model 560-5908-U supplies +12 VDC to the antenna BNC and will support Symmetricom's universal GPS antenna as well as the Down/Up converter.

The GPS-PCI-2U card requires a +12 VDC antenna and may severely damage any antenna that does not support +12 VDC. For non-standard antenna types, contact WARNING Symmetricom for assistance. A connection to an older style +5 VDC antenna will destroy the antenna.

#### 1.2 **Physical Specifications**

The PCI card is a single-slot PCI-compatible short card (6.875 in [17.463 cm] long).

#### 1.3 **Environmental Specifications**

| Operating Temperature: | $0^{\circ}$ to +50°C (+32° to +122°F)                                |

|------------------------|----------------------------------------------------------------------|

| Storage Temperature:   | $-17^{\circ}$ to $+100^{\circ}$ C ( $0^{\circ}$ to $+212^{\circ}$ F) |

| Humidity:              | 95% relative, non-condensing                                         |

#### 1.4 **Power Specifications**

The PCI host computer powers the card. Maximum power consumption is shown below. Model 560-5907-U

+12 VDC @ 100 mA - 12 VDC @ 50 mA + 5 VDC @ 1300 mA

Model 560-5908-U (GPS) with standard Antenna:

+12 VDC @ 200 mA - 12 VDC @ 50 mA + 5 VDC @ 1500 mA

#### 1.5 Antenna Specifications (560-5908-U)

To operate in the GPS Synchronized Generator mode, the unit requires an external antenna. The standard antenna supplied with this option is part number 142-614-50, which includes 50 feet (15.24 meters) of coaxial cable. Cable lengths from 200 feet (60.96 meters) to 1,500 feet (457.2 meters) require the antenna Down/Up Converter option, part number 142-6150.

## Model 560-5908-U supplies +12 VDC to the antenna BNC. Connection to an older +5 VDC antenna will destroy the antenna.

The general specifications for the 142-614-50 antenna are:

| Size:                  | 2.625 in diameter x 1.5 in (6.67 cm dia x 3.81 cm)                        |

|------------------------|---------------------------------------------------------------------------|

| Weight:                | 0.55 lb. (0.250 kg) (including mounting mast)                             |

| Operating Temperature: | $-40^{\circ}$ C to $+70^{\circ}$ C ( $-40^{\circ}$ F to $+158^{\circ}$ F) |

| Storage Temperature:   | $-55^{\circ}$ to $+85^{\circ}$ C ( $-67^{\circ}$ F to $+185^{\circ}$ F)   |

| Humidity:              | 100% condensing                                                           |

| Power:                 | 25 mA @ 12 V (supplied by card)                                           |

The cable specifications for the 142-614 antenna are:

| Туре:       | RG-59                  |

|-------------|------------------------|

| Length:     | 50 feet (15.24 meters) |

| Weight:     | 1.2 lb. (0.545 kg)     |

| Humidity:   | All weather, outdoors  |

| Connectors: | TNC male to BNC male   |

If you have the optional 142-6150 Down/Up Converter antenna, please refer to its manual for specifications. Antenna and Down/Up Converter units are mounted on a 12-inch (30.48 cm) long PVC mast with 3/4-inch (1.9 cm) Male Pipe Thread (MPT) on both ends. The above specified weights include this mounting mast. Unless noted otherwise, increase the above specified sizes by approximately 11.25 inches (28.58 cm) to include the mounting mast.

## 1.6 Signal / Timing Specifications (560-5907-U and 560-5908-U)

Amplitude-Modulated Reference Code Input

| Format:                  | IRIG-B AM (amplitude-modulated) or<br>IRIG-A AM (amplitude-modulated) |

|--------------------------|-----------------------------------------------------------------------|

| Amplitude:               | 0.5 to 10 Vp-p                                                        |

| Impedance:               | Selectable, 10k, 600 $\Omega$ or 50 $\Omega$ to GND                   |

| Ratio:                   | 2:1 to 5:1                                                            |

| Error Bypass:            | 3 frames                                                              |

| Phase Accuracy:          | $<3 \mu s$ with stable input reference                                |

| Phase Compensation:      | $\pm 800 \ \mu s$ in 100 ns steps                                     |

| Oscillator Tuning Range: | 5x10 <sup>-6</sup>                                                    |

| Connector:               | Rear-panel female BNC "CODE IN"                                       |

## DC-shift Reference Code Input

| Format:         | DC-shift IRIG-B002 or                                                                      |

|-----------------|--------------------------------------------------------------------------------------------|

| Format:         | DC-shift IRIG-A002                                                                         |

| Levels:         | RS-422 or TTL                                                                              |

| Impedance:      | Jumper-Select: 120 $\Omega$ or HI (4 k $\Omega$ minimum)                                   |

| Error Bypass:   | 3 frames                                                                                   |

| Phase Accuracy: | <1 µs with stable input reference                                                          |

| Connector:      | Rear-panel D9<br>Pin 3 (+), 4 (-) for RS-422 levels<br>Pin 3 (SIG), 2 (GND) for TTL levels |

## 1.7 External Event / 1 PPS Reference Input

| Active Edge External Event:  | Selectable: Rising or Falling                                   |

|------------------------------|-----------------------------------------------------------------|

| Active Edge 1 PPS Reference: | Rising                                                          |

| Levels:                      | Logic 0: -0.5 to +1.75 VDC                                      |

|                              | Logic 1: +2.25 to 5.0 VDC                                       |

| Impedance:                   | Approximately 2 k $\Omega$                                      |

| Phase Accuracy (1 PPS):      | $<1 \ \mu$ s, typically $<500 \ ns$ with stable input reference |

| Connector:                   | Rear panel D9 subminiature, pin 1                               |

## 1.8 GPS Timing Specifications (560-5908-U)

| Timing Accuracy:   | $< 1 \ \mu s$ to UTC                                                  |

|--------------------|-----------------------------------------------------------------------|

| Position Accuracy: | Latitude, longitude, and elevation 25 meters SEP without SA           |

| Acquisition Time:  | 20 minutes on cold start with power cycle, worst case scenario        |

| Receiver Input:    | Frequency: 1575.42 MHz (L1)                                           |

| Code:              | Coarse Acquisition (C/A)                                              |

| Tracking:          | 8 satellites (4 for solution, 6 reported)                             |

| Connector:         | Rear panel female BNC "ANTENNA"<br>BNC supplies +12 VDC antenna power |

## 1.9 Output Signal Specifications

ACMOS outputs, noted in the following text, provide greater than or equal to 3.0 Vp-p into  $50 \Omega$

## 1.9.1 Amplitude-modulated Generator Code Output

| Format:      | IRIG-B122                                          |

|--------------|----------------------------------------------------|

| Amplitude:   | Factory set for 3 Vp-p into 600 $\Omega$ to ground |

| Fixed Ratio: | 3:1                                                |

| Connector:   | Selectable on rear-panel "CODE OUT" BNC            |

## 1.9.2 IRIG-B DC Generator Code Output

| Format:    | DC-Shift IRIG-B002                                                               |

|------------|----------------------------------------------------------------------------------|

| Levels:    | RS-422 on D9, ACMOS on BNC                                                       |

| Connector: | Rear-panel D9 subminiature, pin 8 (+), pin 9 (–) or selectable on "CODE OUT" BNC |

## 1.9.3 Time Compare Output

| Resolution:   | 1 μs                                                                             |

|---------------|----------------------------------------------------------------------------------|

| Pulse Width:  | 1 ms                                                                             |

| Compare Mask: | Milliseconds through hundreds of days                                            |

| Levels:       | ACMOS                                                                            |

| Timing:       | Rising edge on time                                                              |

| Connector:    | Selectable or rear-panel D9 subminiature, pin 6; or selectable on "CODE OUT" BNC |

## 1.9.4 1 PPS Output

| Rate:       | 1 PPS                                                              |

|-------------|--------------------------------------------------------------------|

| Duty Cycle: | 50%                                                                |

| Amplitude:  | ACMOS                                                              |

| Timing:     | Rising edge on time                                                |

| Connector:  | Rear-panel D9 subminiature, pin 5; or selectable on "CODE OUT" BNC |

## 1.9.5 Rate Generator Output

| Timing:           | Rising edge on time                                                             |

|-------------------|---------------------------------------------------------------------------------|

| Selectable Rates: | 1 PPS, 10 PPS, 100 PPS, 1k PPS, 10k PPS,<br>100k PPS, 1 MPPS, 5 MPPS or 10 MPPS |

| Levels:           | ACMOS                                                                           |

| Connector:        | Rear-panel D9 subminiature, pin 7; or selectable on "CODE OUT" BNC              |

| 1.9.6          | Rate Synthesizer Output                                           |                                                                                                                                                                                                                 |  |

|----------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                | Timing:                                                           | Selectable Rising or Falling on-time edge                                                                                                                                                                       |  |

|                | Rates:                                                            | 1 PPS to 1 MPPS in 1 PPS increments                                                                                                                                                                             |  |

|                | Jitter:                                                           | 30 ns                                                                                                                                                                                                           |  |

|                | Levels:                                                           | ACMOS, squarewave                                                                                                                                                                                               |  |

|                | Connector:                                                        | Selectable on rear-panel D9 subminiature, pin 6; or selectable on "CODE OUT" BNC                                                                                                                                |  |

| 1.10           | General Specifications                                            |                                                                                                                                                                                                                 |  |

|                | SyncGen Timing Accuracy:                                          | $<3 \mu s$ - IRIG-A or B (AM) modes                                                                                                                                                                             |  |

|                |                                                                   | <1 µs - IRIG-A or B (DC) modes                                                                                                                                                                                  |  |

|                |                                                                   | <1 µs - 1 PPS mode                                                                                                                                                                                              |  |

|                |                                                                   | <1 µs to UTC-USNO - GPS mode (560-5908-U)                                                                                                                                                                       |  |

|                | TCVCXO disciplined oscillator:                                    | 10.000                                                                                                                                                                                                          |  |

|                | Frequency:                                                        | 10.000 MHz                                                                                                                                                                                                      |  |

|                | Frequency Stability (w/ref): $<1x10^{-7}$ , typically $5x10^{-8}$ |                                                                                                                                                                                                                 |  |

|                | Aging:                                                            | <1 PPM/Year                                                                                                                                                                                                     |  |

|                | Leap Year:                                                        | Automatically resets to day 1 after day 365 in standard years and after day 366 in leap years.                                                                                                                  |  |

|                | Leap Second:                                                      | Automatically handles leap seconds in GPS mode (560-5908-U). User-programmable on day of occurrence in SyncGen mode.                                                                                            |  |

|                | Interrupts:                                                       | Single PCI Interrupt                                                                                                                                                                                            |  |

| Lock Criteria: |                                                                   |                                                                                                                                                                                                                 |  |

|                | IRIG AM Codes (A, B):                                             | One input on-time mark within 600 ns of the output<br>on-time mark AND eight consecutive input on-time<br>marks all of which are less than 1.5 @s from the output<br>the aggregate error is less than eight @s. |  |

|                | IRIG DC Codes PPS, GPS:                                           | One input on-time mark within 300 ns of the output<br>on-time mark AND eight consecutive on-time marks in<br>which none have an error of greater than 500 ns.                                                   |  |

|                | Unlock Criteria:                                                  |                                                                                                                                                                                                                 |  |

|                | IRIG AM Codes A, B:                                               | Five out of ten on time marks have an error of greater than three $\mu$ s.                                                                                                                                      |  |

|                | DC Codes PPS, GPS IRIC                                            | G DC:                                                                                                                                                                                                           |  |

|                |                                                                   | Five out of ten on time marks have an error of greater than one $\mu$ s.                                                                                                                                        |  |

Lock Time:

Sync Gen (non-GPS): Minimum 15 seconds Maximum two minutes

## 1.11 Factory Defaults

## 1.11.1 560-5907-U/560-5908-U Configuration

The following are the factory default settings for the PCI card. This configuration is restored when the Restore Factory Defaults bit is set at register location 0x12C (bit 3).

| 1. Mode                  | Generator, on                                                         |

|--------------------------|-----------------------------------------------------------------------|

| 2. DAC value             | 8000H                                                                 |

| 3. Year                  | 2003                                                                  |

| 4. Rate Generator        | 1 kPPS, on                                                            |

| 5. Time Zone sign        | +                                                                     |

| 6. Time Zone offset      | 0                                                                     |

| 7. Phase Compensation    | 0                                                                     |

| 8. Rate Synthesizer      | 60 PPS, off                                                           |

| 9. Rate Synthesizer edge | Rising on time                                                        |

| 10. Event Time Capture   | External Event                                                        |

| 11. Event Trigger edge   | Rising                                                                |

| 12. Code Out BNC         | IRIG-B AM                                                             |

| 13. Time Compare value   | $DAY = 1$ , $hr = 0$ , $min = 0$ , $sec = 0$ , $ms = 0$ , $\mu s = 0$ |

| 14. Time Compare mask    | B0 (provides 100 PPS rate)                                            |

## 1.11.2 560-5907-U/560-5908-U Factory Installed Hardware Jumper Configuration

- JP1: OFF This jumper is used for IRIG-A or B with RS-422 input and provides  $120 \Omega$  AC termination. This jumper should be OFF when using IRIG DC input mode.

- JP3: Termination for Amplitude Modulated reference code input. JP3-2 to JP3-3 (10 k  $\Omega$  to GND)

JP3-1 to JP3-2 (600  $\Omega$  to GND) - Factory Default

JP3-3 to JP3-4 (50  $\Omega$  to GND)

## 9-Pin Male D Connector (P1) Pin Assignment

| PIN | Description                                  |

|-----|----------------------------------------------|

| 1   | External Event / 1 PPS Input                 |

| 2   | GND                                          |

| 3   | DC Reference Code Input + or TTL             |

| 4   | DC Reference Code Input -                    |

| 5   | 1 PPS Output                                 |

| 6   | Selectable: Time Compare or Rate Synthesizer |

| 7   | Rate Generator Output                        |

| 8   | DC Generator Code Output + or TTL            |

| 9   | DC Generator Code Output -                   |

## Installation

## 2.1 Installing the Card

This section contains installation instructions for the Model 560-5907-U and 560-5908-U cards, and information regarding operating modes and the use of registers to configure the card. The Model 560-5908-U has the additional feature of GPS mode, which has the ability to automatically synchronize the card to UTC time.

## 2.1.1 Installation

Unpack the card and carefully inspect it for shipping damage. Report any damage to the carrier immediately.

Record the card's serial number.

With the computer's power turned OFF, install and secure the card in an empty PCI card slot. Fabricate any required I/O cables and connect them to the appropriate connectors.

If Windows does not display the "New Hardware Found" message automatically after starting Windows, install the hardware manually using the Add/Remove Hardware program in Windows Control Panel.

## 2.1.2 Antenna Location and Installation (GPS only)

When selecting a site for the antenna, find an outdoor location that provides full 360-degree visibility of the horizon. In most cases, this means locating the antenna as high as possible. Any obstruction will degrade unit performance by blocking the satellite signal

or causing a reflection that cancels some of the signal. Blocked signals can *significantly* increase the time for satellite acquisition, or prevent acquisition all together.

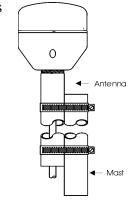

## Mast Mounting

Mast top mounting is the preferred mounting method and special brackets are provided to mount the antenna to a pipe or the peak of a building. The antenna mounting mast should be 2-inch (5.08-cm) water pipe or conduit. The mast must be rigid and able to withstand high winds without flexing. Guy wires may be used to stabilize a mast longer than 10 ft. (3.048 m)

Multipath cancellation is caused by reflected signals that arrive at the antenna out of phase with the direct signal. Reflective interference is most pronounced at low elevation angles from 10 to 20 degrees above the horizon. You may extend mast height to prevent multipath cancellation. The antenna should be at least 3.28 ft. (1.0 m) from a reflecting surface.

## Use of a Splitter

To run multiple units with a single 12 VDC antenna, use a splitter. Do *not* use a BNC "T" connector.

## Lead-In Cable

The L1 GPS antenna is designed to operate with up to 200 ft. (60.96 m) of RG-59 coax cable. The optional Down Converter is designed to operate with up to 1,500 ft. (457.2 m) of RG-58 coaxial cable.

## 2.2 TTPciPanel Software Requirements and Installation

Symmetricom PCI cards come with the Symmetricom TTPciPanel (TTPciPanel.exe) software for Windows NT 4.0, 2000, XP. TTPciPanel provides basic PCI card operations, and can synchronize the Windows clock to the PCI card's time at a user-configured interval.

TTPciPanel is an example program created using the SDK (Software Development Kit) provided on the CD. Using the SDK, a programmer can further customize TTPciPanel or create new software applications for the PCI card. It is presumed that the customer knows how to create a GUI using the provided SDK software.

## 2.2.1 Minimum System Requirements

Pentium III, 300 MHz or faster PC with one free PCI slot

Windows NT 4.0, 2000, XP

2MB disk space

## 2.2.2 User Notes

TTPciPanel is an easy to use and understand program. If you have read the PCI board manual, most fields and their function are self explanatory. When in a control field and data is changed, pressing the *ENTER* or *TAB* buttons to the next control field will write the changes made into board memory. If you press *ESC*, the change made is lost and the original value returns.

Certain functions on the menus are only available with certain model PCI cards. Some functions, fields or menus may be grayed out or otherwise not usable. For instance, the *Save in Flash* function in the drop-down menu is only available with PCI boards model 560-5907-U and 560-5908-U.

Use *Save DAC to Flash* to quicken the card's lock time. When the card has been locked and the DAC saved, the setting will then be used as the default offset at power up.

## 2.2.3 Optional Software Development Kit

To develop applications for Symmetricom PCI cards you can order the optional Software Development Kit, SDK for PCI. This SDK also supports all Symmetricom PCI boards. Symmetricom offers this to our customers who do not wish to write their own software driver. The SDK provides the user with all the functions necessary to control and read the time from the board. This allows the user to create his own customized code for use with Symmetricom boards with a minimum of time and effort. Contact Symmetricom or visit http://www.Symmetricom.com for further detail.

## 2.2.4 Installing TTPciPanel

# If you currently have Symmetricom's TimeServer32 program installed on your system, you must uninstall it before installing TTPciPanel.

Insert the CD into the computer's optical media drive. Autorun spins the CD and launches the InstallSheild Wizard for TTPciPanel. Perform a default installation by clicking **Next** or **Yes** in response to the prompts and restart the computer.

If Autorun does not run, open the CD in Windows Explorer and double-click TTPciPanel\_NT\_2K.exe from the following files on the CD:

- AUTORUN.INF

- ReadMe.txt

- TT\_GPS.sys

- TTPCI\_W2K.inf

- TTPciPanel\_NT\_2K.exe

## 2.2.5 Upgrading from TTPciPanel

To upgrade from TTPciPanel version 4.0 to version 6.2 complete the following steps (in Windows 2000):

From the Control Panel, select System, Hardware tab, and the Device Manager button.

In Device Manager, under System Devices, select TrueTime (GPS) Synchronized Time Adapter. Make note of the model number: 560-5907 or 560-5908.

Right-click the device and select **Properties**.

Under the **Driver** tab, select **Update Driver**.

In the Upgrade Device Wizard, select Next and Display a list of the known drivers so that I can choose a specific driver.

Click the **Have Disk** button to launch the **Install from Disk** window, then **Browse** to the driver CD, open the **TTPCI\_W2K.inf** file, and click **OK** to return to the Update Device Driver Wizard.

A list of device drivers will appear. Select the driver for the 560-5908 or 560-5907 depending on the model number noted earlier, and then complete the installation wizard. Windows should now have the proper linkage to the updated device driver.

## 2.2.6 Starting TTPciPanel

From the Windows **Programs** menu, select **TrueTime - TTPciPanel - TTPciPanel**. The TTPciPanel user interface appears (Figure 2-1 on page 18).

| ard Time (UTC) — | Lock                 | Status<br>Never Locked | C | ~                    |  |

|------------------|----------------------|------------------------|---|----------------------|--|

|                  |                      |                        |   | etricom <sup>®</sup> |  |

| Device Genera    | I Time GPS Eve       | ents                   |   |                      |  |

| - Device Acc     | A46                  |                        |   |                      |  |

|                  | 308 @ Bus: 0 Slot: 0 |                        |   |                      |  |

|                  | Vrite Access         | Open                   |   |                      |  |

|                  | 🔽 Read Access        | Close                  |   |                      |  |

| -                |                      |                        |   |                      |  |

| - Revision Sta   |                      | are Revision           |   |                      |  |

|                  | board nimw           |                        |   |                      |  |

|                  |                      |                        |   |                      |  |

|                  |                      |                        |   |                      |  |

|                  |                      |                        |   |                      |  |

Figure 2-1 TTPciPanel 's appearance when opened.

Under the **Device** tab, **Device Access** lists the device or devices present that TTPciPanel interoperates with. Select a device and click **Open**.

TTPciPanel connects to the device and displays device information.

**Note**: If other devices, such as the 560-5900 or 560-5901 cards, are present, and you select them in the Device Access menu, a number of features in TTPciPanel will be blank or disabled because those cards to not interoperate with those specific features. If a 560-5908-U card is installed, all items should be available. The 560-5900 or 560-5901 card does not translate. The 560-5907-U or 560-5908-U card can translate. GPS related functions will not be accessible if GPS is not being used.

## 2.3 Quickstart Guide to Operating TTPciPanel

Verify that the card is connected to the appropriate reference source input. For example, with the 560-5908 GPS-PCI-2U, make sure the antenna cable is connected to the **Antenna BNC** connector on the rear of the card.

Under the **Device** tab, select a specific card from the **Device Access** menu and click the **Open** button.

Under the **General Tab**, select the appropriate **Sync Source** for the type of card you are using. For example, with the 560-5908 GPS-PCI-2U, select GPS in the Sync Source menu. The device starts locking to the reference source provided.

For **Output BNC Source**, select the type of output to generate on the **Code Out BNC** on the rear of the card.

If you're testing the card and don't need it to lock to the reference source, you can set the time manually using **Set Board Clock (UTC)** under the **Time** tab.

## 2.4 TTPciPanel Screen Descriptions

## 2.4.1 Main Panel

Title Bar, the blue area located at the top of the TTPciPanel window.

- When no device is selected in Device Access, the title bar states "TTPciPanel Demo".

- When a device is selected in Device Access and opened, the title bar states the model, bus, slot, and access level

**Board Time** states the UTC date and time of the selected device. When no device time is available, this field is blank.

**Lock Status** provides the following lock status as well as the names of the reference source:

- Never Locked (Gray): the device has not locked to a reference source since being started

- Unlocked (Red): A device is selected, but has not locked to a reference source.

- Locking (Yellow): A device is selected, and is locking to a reference source.

- Locked (Green): A device has been selected and is locked to the reference source.

## 2.4.2 Device Tab

**Device Access**: Use Device Access to select the specific card TTPciPanel will interoperate with.

**Write Access**: Selecting the check box for Write Access enables TTPciPanel to write information to the card. To protect against accidental changes of the configuration in TTPciPanel, deselect Write Access. In most cases, Write Access is selected.

**Read Access**: Selecting the check box for Read Access enables TTPciPanel to read information from the card. This box should be selected in almost all cases.

**Open**: Clicking the Open button activates the card selected in Device Access. The other tabs are not available until Open has been clicked.

Close: Clicking the Close button closes the TTPciPanel application.

**Revision Status** displays the **Board Firmware Revision** number, which is useful when addressing technical support questions to Symmetricom Customer Assistance or evaluating whether to upgrade the firmware. (Note: this information is not available from a 560-5900 or 560-5901 card.)

## 2.4.3 General Tab

**Sync Source**: use this menu to select an appropriate reference source (e.g., GPS, 1 PPS, IRIG) that is available on the device.

**Note**: With the 560-5900 and 560-5901 card, an input source (Sync) can be selected. However, the Output BNC Source is always IRIG AM Timecode. With the 560-5907-U and 560-5908-U card, both an input and Output BNC Source source can be selected.

Output BNC Source: Select the type of output signal to generate on the Code Out BNC.

**Phase Compensation**: Advance (positive values) or retard (negative values) output signal by the value specified in microseconds.

**Board Status** shows the status of the card's memory, DAC, and clock functions. It also displays the DAC value applied to discipline the card's oscillator to the reference source.

## 2.4.4 Time Tab

**PC Clock Setup**: To synchronize the PC clock with the Board Time on a periodic basis, select the **Update PC clock every:** checkbox and select the interval (minute, hour, or day). TTPciPanel will only update the PC clock when it has a valid reference.

**Local Time** shows the Board Time plus the Standard Time Zone and Daylight Saving Time offset provided by the Windows clock settings.

**Set Board Clock**: Use the fields to set the Year, Month, Day, Hour, Minute, or Second of the Board Time manually. When a reference source is available, the time from the reference source overrides these settings. GPS overrides all the fields. IRIG overrides all the fields except the year field.

**Leap Second**: Click the Add Leap Second at UTC Midnight checkbox if the current year is a leap year. **Note**: this option is not valid.

See "Configuration #2 Register" on page 36.

## 2.4.5 GPS Tab

When the GPS antenna is operational and locked, the following information is provided:

- Satellites: PRN, Signal strength

- Antenna status: OK or Open

- Position: Latitude, Longitude, and Elevation in Meters.

## 2.4.6 Events Tab (See 3.3.16 for details)

**Events Section**: Use the Trigger Source drop-down to select external/internal source.Use the Trigger Edge, Event Time, or Enable Interrupt as needed.

**Synthesizer Section**: Use the Frequency, or On Time Edge drop-down menu to select from. The Run/Stop button must be in the "Run" position for the synthesizer to be active. Check the Enable Interrupt box to enable the Interrupt.

**Rate Generator**: In the Rate Generator section, use the Disable drop-down to select from 1 through 10K PPS. Check the Enable Interrupt box to enable the Interrupt.

**Time Compare**: Using the various drop-down menus, the user is able to precisely select the time needed for their own purpose. These are self-explanatory. Enable Interrupts as necessary by checking the box.

Installation

## Operation

## 3.1 General Operation

The following paragraphs describe the operation of the PCI card. They describe the operating modes, the various registers used, and how to control and configure the card. All register addresses are specified as an offset from the PCI Memory Base Address. Most features on the card may be used simultaneously. Any constraints on a specific feature in terms of its compatibility will be discussed.

The PCI card operates in either Generator Mode or Synchronized Generator Mode supplying precise time (100's of nanoseconds through thousands of years) to the host computer. The card cannot be set prior to 2000, or beyond the year 2039.

In the Generator mode the time may be started stopped and preset via the PCI bus. In this mode, the Generator time accuracy is a function of the drift rate of the on-board oscillator.

When operating as a Synchronized Generator, the output signals are synchronized to timing reference. The PCI card phase locks to the timing reference and controls the on-board oscillator to remove frequency errors. If the timing reference is lost, the PCI card continues to increment time and output timing signals based upon the previously steered on-board oscillator's frequency (flywheeling).

## 3.1.1 Time Preset

Year information is not encoded in the time code reference but is available over the PCI bus. To set the year, use the Time Preset function. Year data is necessary to handle end-of-year rollover correctly for leap years. Year information is saved in EEPROM and automatically increments at the end of each year.

## 3.1.2 Generator Mode

At turn-on, the time is based on the PCI card's real-time-clock (RTC) while the frequency is derived from the on board oscillator. The RTC is used by the card to keep time when the card's power is lost. It has the ability to run (card not powered) for over two days. The RTC is accurate to approximately two seconds per day with respect to the last synchronizing reference once the power is restored.

In Generator mode, the time may be preset and the accumulation of time may be started or stopped via the Configuration Register #1. When in this mode, the PCI card runs at the rate of the on-board oscillator (timing will drift with the oscillator error).

Use the Generator mode whenever a timing source is not available or when it is necessary to start and stop the time and timing outputs (with the exception of the Rate Synthesizer). When using this mode, it is preferable to have previously used the Synchronized Generator mode connected to a timing source with known frequency accuracy, allowed the PCI card to lock to the source, and saved the DAC setting. If a synchronized DAC setting has not been previously saved, the default DAC setting is used.

## 3.1.3 Synchronized Generator Mode

The Synchronized Generator mode operates as a Generator that is synchronized to an external time reference. The Synchronized Generator phase locks to the time reference and disciplines the oscillator to remove frequency errors. If the reference code is lost, the Synchronized Generator continues to increment time based upon the disciplined on-board oscillator.

The Model 560-5907-U (PCI-SG-2U) card may be synchronized by one of the following input references:

| IRIG-B AM | Year entry required                            |

|-----------|------------------------------------------------|

| IRIG-A AM | Year entry required                            |

| IRIG-B DC | Year entry required                            |

| IRIG-A DC | Year entry required                            |

| 1 PPS     | Time entry from years through seconds required |

The Model 560-5908-U (GPS-PCI-2U) card may be synchronized by any of previously listed references or by:

| GPS Automatic UTC time |

|------------------------|

|                        |

## 3.2 PCI Card Control/Status Registers (Overview)

- 1. The Software Time Capture Registers are updated by writing to the low-order Freeze Register. The Time registers contain thousands of years through 100's ns. The Position Registers, used only in the GPS Synchronized mode, contain the GPS position (longitude, latitude, and elevation).

- 2. The Configuration Registers control the configuration of the PCI card. They are used to select the mode of operation, to select the Synchronized Generator reference, to start and stop the Generator, to preset the Generator time, to preset GPS position, to set Daylight Saving Time (DST) function, to set Event active edge, to select IRIG input codes, to set the Rate Generator output and to set the Rate Synthesizer output.

- 3. The Time Zone Offset Register is used to convert UTC time to local time. Local time is used for software time capture and IRIG-B output. This feature is not available with TTPciPanel.

- 4. The Phase Compensation/Factory Calibration Registers are used to adjust the phase difference between the Synchronized Generator amplitude-modulated reference input and the time outputs to compensate for system delays.

- 5. The Diagnostic Register contains the results of the internal diagnostic tests performed at power-up and during normal operation.

- 6. The Event Time Registers are used to capture the time of an event. The event may be selected to be External Event or one of the following PCI card generated signals; Rate Generator, Rate Synthesizer or Time Compare.

- 7. The Time Compare Registers are used to program the Time Compare output.

- 8. The Hardware Control and Hardware Status Registers handle PCI card interrupt sources and status flags for event, time compare, rate generator, rate synthesizer, and antenna open/short.

- 9. The Position Preset Registers are used to preset a new position when in GPS Synchronized mode (Model 560-5908-U only).

- 10. The Signal Level Registers contain the satellite numbers and signal levels of up to six satellites when in the GPS Synchronized mode (Model 560-5908-U only).

- 11. The Preset Time Registers are used to set time to the level allowed for the selected modes: ms for Generator, seconds for 1 PPS Sync, Years for IRIG Sync, the GPS Week Number Epoch for GPS Sync.

- 12. The Rate Synthesizer Register is used to set frequency output rates.

## 3.3 PCI Card Registers

Data registers on the PCI card are mapped into PCI Memory Space and are used to control, configure and report information on the PCI card. All locations are described by the offset from the PCI Base Address Register 2 (the 3rd Register).

## 3.3.1 PCI Configuration Header Region

The PCI has a block of 64 configuration double words reserved for the implementation of its configuration registers. The first 16 double words are predefined by the PCI specification. This area is referred to as the Configuration Header Region.

To determine what devices are present, system software scans the PCI bus for the Vendor ID in each possible PCI slot. To uniquely identify the PCI card, the following registers are:

| Device ID:           | 0x9050                 |

|----------------------|------------------------|

| Vendor ID:           | 0x10B5                 |

| Subsystem Vendor ID: | 0x12DA                 |

| Subsystem ID:        | 0x5907 or 0x5908 (GPS) |

## 3.3.2 PLX 9050 Local Configuration Registers

The PCI card's interface chip (PLX9050) has a block of 32 double word registers reserved for local configuration purposes. This area is referred to as the Local Configuration Registers and is physically mapped both to memory and to I/O addresses at run time. The memory mapped versions' base address is located at 0x10 in the Configuration Header Region (see above) and the base address for the I/O mapped version is at 0x14. Either I/O or memory read or write cycles may be used to access the LCRs. Normally, you will only access one register, the INTCSR Register, at location 0x4C.

# C

# Writing to other registers in this region runs the risk of locking up your computer or causing other unusual symptoms, requiring a power-cycle to recover.

Writing a value of xxxxx48h to this register (0x4C) will enable the PLX9050 chip to pass along interrupts from the card if they are enabled elsewhere. The card is normally shipped with this value pre configured, however, it is possible that this value has been changed from the default and you will need to know how to set it back. Note that the value xxxxx08h will disable all interrupts.

## 3.3.3 Hardware Control Register

This register is used to control the interrupts and clear the signal status bits that are generated by the PCI card. Note that the status bits are generated regardless of the state of the interrupt mask bits in this register.

Select PCI interrupt sources via the Hardware Control Register located at offset 0xF8. Any combination of sources in the following table may be selected. The Event, Time Compare, Rate Generator and Rate Synthesizer flags are always available in the Hardware Status Register and can be un-masked, via bits 3, 4, 5 and 7 to generate interrupts. The Status bits are cleared via bits 0, 1, 2 and 6 (writing a 1 to these bits generates a 1-cycle clear pulse). In addition to this register, you may also need to program the INTCSR register at offset 0x4C in the PLX9050 chip (see prior section PLX 9050 Local Configuration Registers).

| PCI Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bits 7-4                                          | Bits 3-0  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------|--|--|

| 0XF8 <sup>P</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Interrupt and Status Flag<br>Control <sup>1</sup> |           |  |  |

| 0xF9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Undefined                                         | Undefined |  |  |

| 0xFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Undefined                                         | Undefined |  |  |

| 0xFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Undefined                                         | Undefined |  |  |

| Notes:<br>P: PCI Quad Address (base address of four ascending contiguous bytes)<br><b>1: Interrupt and Status Flag Control</b><br>Bit 7: Rate Synthesizer Interrupt Mask (0=Interrupt Disabled, 1= Enabled<br>Bit 6: Rate Synthesizer Status Clear<br>Bit 5: Rate Generator Interrupt Mask (0= Interrupt Disabled, 1= Enabled)<br>Bit 4: Time Compare Interrupt Mask (0=Interrupt Disabled, 1= Enabled)<br>Bit 3: Event Interrupt Mask (0= Interrupt Disabled, 1= Enabled)<br>Bit 2: Rate Generator Status Clear<br>Bit 1: Time Compare Status Clear<br>Bit 0: Event Status Clear |                                                   |           |  |  |

| All status clear bits operate the same. When a 1 is written to the status clear bit, the corresponding bit at location 0xFE (Status Flag) is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |           |  |  |

### Hardware Control Register

## 3.3.4 Software Time Capture Register

This register is used to obtain a software time capture from the card. In order to obtain time, write any value to location 0xFC. This causes the current time, compensated by the local offset and daylight saving time, to be written to this register. The time is stable and ready to read when the Software Time Ready bit is set in the Status Flags location (0xFE). Writing location 0xFC causes the Software Time Ready bit to be cleared. The time delay from the write of 0xFC to the Ready bit being set is a maximum of 150 ns. Time can be read immediately following the write to 0xFC (not waiting for the status flag). The Time Registers start at offset 0xFC and contain packed BCD data, except for the Status bits.

| PCI Offset         | Bits 7 – 4                  | Bits 3 – 0                |

|--------------------|-----------------------------|---------------------------|

| 0xFC <sup>P1</sup> | Tens microseconds           | Unit microseconds         |

| 0xFD               | Unit milliseconds           | Hundreds microseconds     |

| 0xFE               | Antenna Status <sup>2</sup> | Status Flags <sup>2</sup> |

| 0xFF               | 100's of nanoseconds        | Undefined                 |

| 0x100 <sup>P</sup> | Hundreds milliseconds       | Tens milliseconds         |

| 0x101              | Tens seconds                | Unit seconds              |

| 0x102              | Tens minutes                | Unit minutes              |

| 0x103              | Tens hours                  | Unit hours                |

| 0x104 <sup>P</sup> | Tens days                   | Unit days                 |

| 0x105              | Lock Status <sup>3</sup>    | Hundreds days             |

| 0x106              | Tens years                  | Unit years                |

| 0x107              | Thousands years             | Hundreds years            |

Notes: Time Nibbles are BCD, status nibbles are bits

P: PCI Quad Address (base address of four ascending contiguous bytes)

## 1: Writing any value to location 0xFC updates time and position

### 2: Antenna/Status Flags

The explanation for these two nibbles is contained in the following Hardware Status Register section

### 3: Lock Status

Bit 7: Undefined

Bit 6: Phase Locked to Input REF (0 = Not Locked, 1 = Locked). Locked = timing specification is met.

Bit 5: Input Valid (0 = Not Valid, 1 = Valid). Valid = Time is obtained from reference and is correct.